Aleksandr Sidun

Aleksandr SidunComparator

This is a behavioral analog comparator that outputs VDD when the non-inverting input (inp) exceeds the inverting input (inn), and 0 V otherwise — ideal as a decision element in SAR ADC control logic, zero-crossing detectors, or overvoltage-protection circuits. t_delay models propagation delay and t_edge models rise/fall time, allowing you to approximate realistic comparator speed without a transistor-level model. The built-in $bound_step call prevents the simulator from stepping over fast transitions; comment it out if simulation speed is a concern and transitions are not critical. A typical use-case is the comparison stage in a SAR ADC behavioral model where the bit-cycling logic depends on clean, timely digital decisions from an analog subtraction.

This article contains Verilog-A model for a comparator.

Usage:

- Create a new cell in Library Manager named comp and select cell type Verilog A;

- Copy and paste the code provided;

- Specify VDD variable to be the maximum output voltage of the comparator;

- Specify t_edge and t_delay variables to be the rising/falling time and delay of the output waveform;

- Perform Check and Save;

- A cell symbol will be created;

- Instantiate comp cell into your design;

- Perform Check and Save and run the simulation.

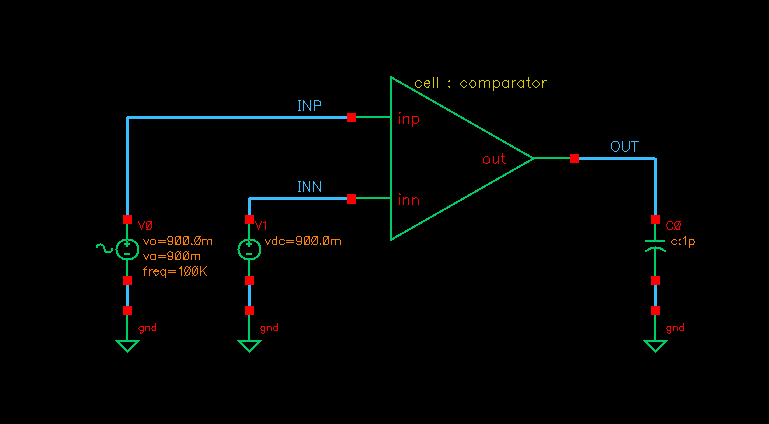

Comparator testbench

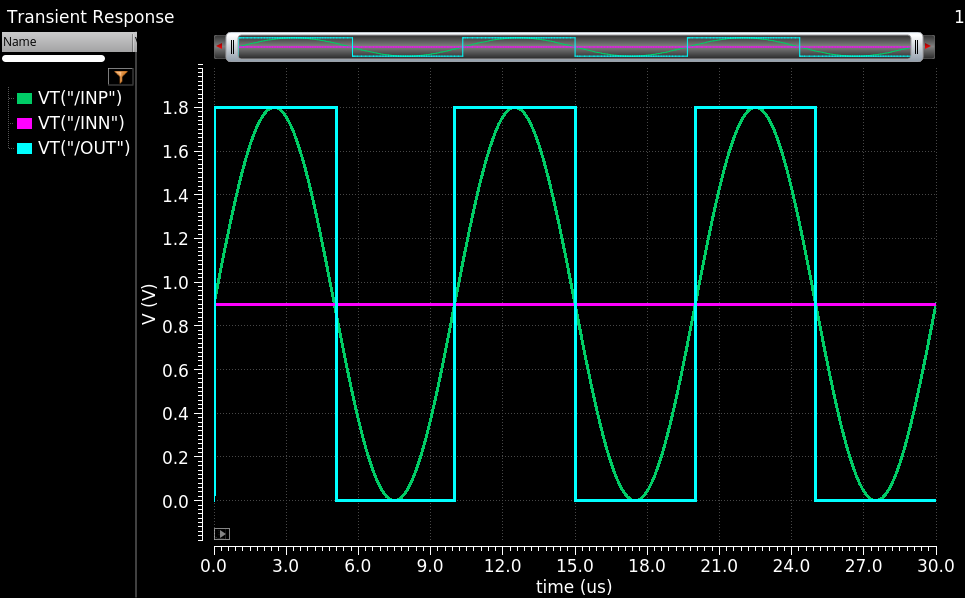

Comparator simulation result

Cell name: comparator

Model type: Verilog-A

1// Comparator model

2// Author: A. Sidun

3// Source: AnalogHub.ie

4

5`include "constants.vams"

6`include "disciplines.vams"

7

8module comparator (inp, inn, out);

9 input inp, inn;

10

11 output out;

12

13 electrical inp, inn, out;

14

15 parameter real VDD = 3.3; // Output voltage during high state

16 parameter real t_delay = 1e-9; // Propagation delay

17 parameter real t_edge = 100e-12; // Rise and fall times

18

19 analog begin

20 V(out) <+ VDD * transition(V(inp) > V(inn), t_delay, t_edge);

21 $bound_step(1/(2*t_delay)); // comment this option if the sim is too slow

22 end

23endmodule