Aleksandr Sidun

Aleksandr SidunDigital-to-Analog (DAC) Verilog-A model

This is a behavioral N-bit digital-to-analog converter that reconstructs an analog voltage from a parallel binary input bus, sampled on a configurable clock edge. It is most useful in mixed-signal testbenches where a digital pattern source (counter, encoder, or static code) needs to drive an analog circuit — for example, sweeping through codes to produce a staircase ramp into a filter or amplifier. The output voltage maps linearly between vmin and vmax; vdd/vss define the input logic levels and thresh sets the decision threshold. Resolution is set by the bits macro, and td/tt model realistic clock-to-output latency. Pair it with the ADC model in a loopback testbench to validate a complete digital-in → analog → digital-out signal path.

This article contains Verilog-A model for a Digital-to-Analog Converter (DAC).

Usage:

- Create a new cell in Library Manager named DAC and select cell type Verilog A;

- Copy and paste the code provided;

- Modify bits variable to define DAC resolution;

- Specify vmin and vmax variables to define the input signal swing;

- Specify vdd and vss variables to define output voltage levels;

- Specify tt and td variables to define rising/falling edge times and output signal delay;

- Specify dir variable to be +1 for rising and -1 for falling clock edge triggering;

- Perform Check and Save;

- A cell symbol will be created;

- Instantiate DAC cell into your design;

- Perform Check and Save and run the simulation.

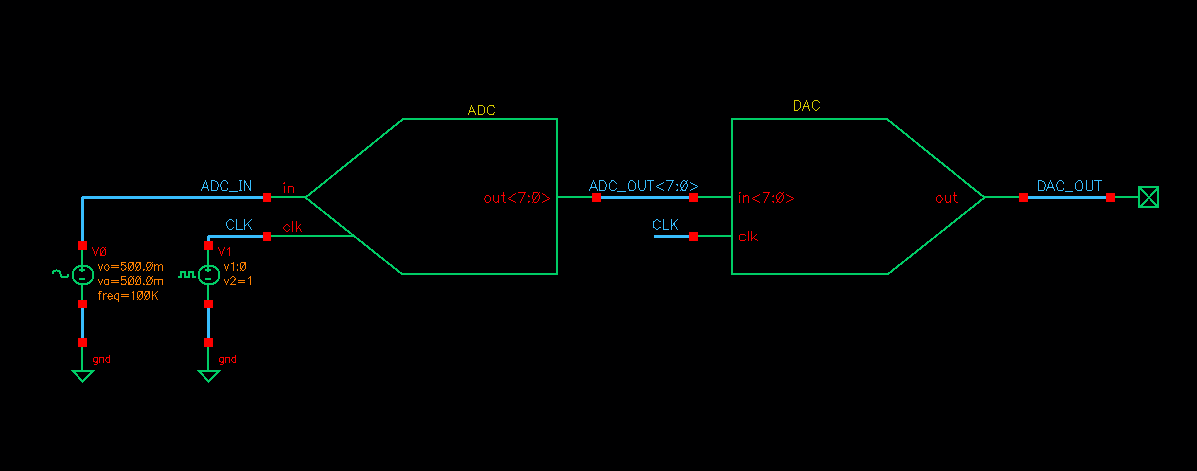

ADC-DAC testbench

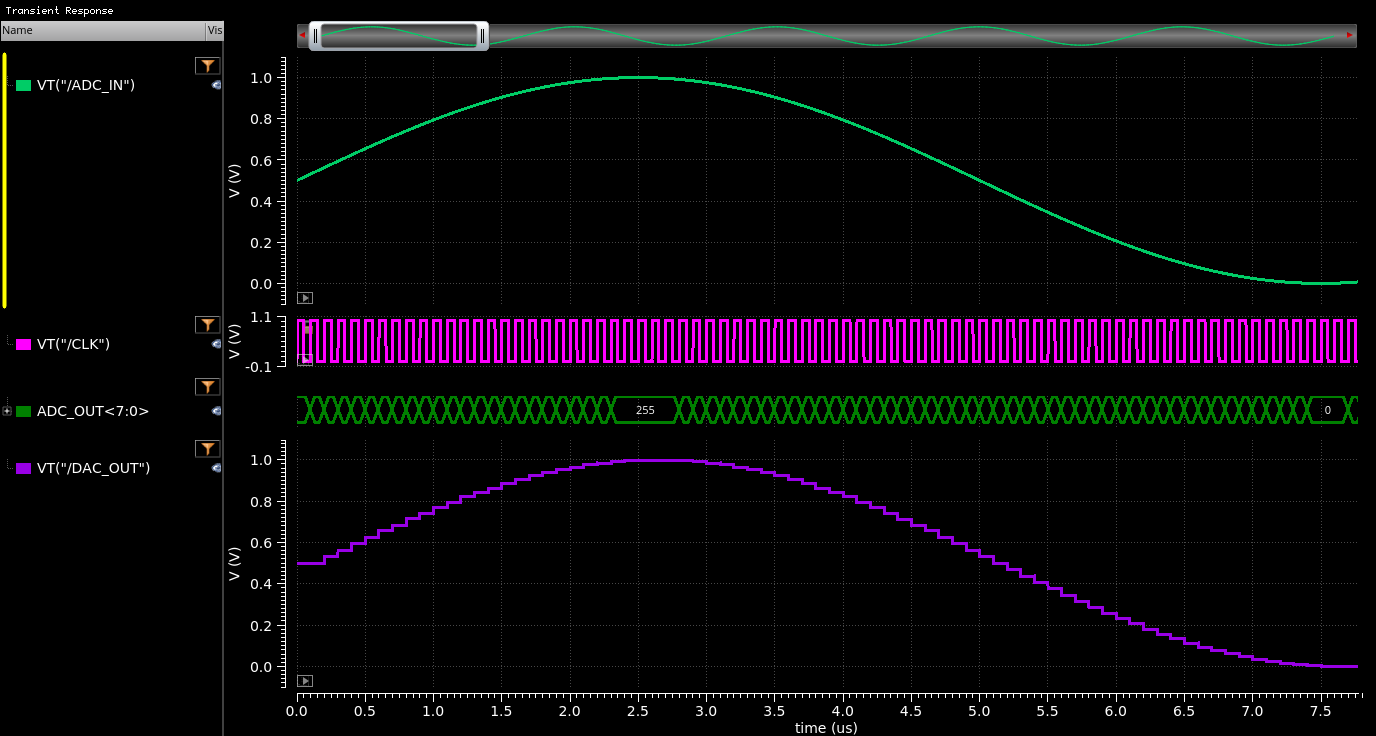

ADC-DAC simulation result

Cell name: DAC

Model type: Verilog-A

1// N-bit Digital to Analog Converter

2// LSB is <0>

3// Change binary_bits variable for your needs!

4// Author: A. Sidun

5// Source: AnalogHub.ie

6

7`include "constants.vams"

8`include "disciplines.vams"

9`define bits 12 // define number of binary bits here

10

11module DAC(out, in, clk);

12 parameter real vmin = 0.0; // minimum input voltage (V)

13 parameter real vmax = 1.0 from (vmin:inf); // maximum input voltage (V)

14 parameter real td = 0; // delay from clock edge to output (s)

15 parameter real tt = 0; // transition time of output (s)

16 parameter real vdd = 5.0; // voltage level of logic 1 (V)

17 parameter real vss = 0; // voltage level of logic 0 (V)

18 parameter real thresh = (vdd+vss)/2; // logic threshold level (V)

19 parameter integer dir = +1 from [-1:1] exclude 0;

20 // 1 for trigger on rising edge

21 // -1 for falling

22 localparam real fullscale = vmax - vmin;

23

24 output out;

25 input [`bits-1:0] in;

26 input clk;

27 voltage out, clk;

28 voltage [`bits-1:0] in;

29 real aout;

30 integer weight;

31 genvar i;

32

33 analog begin

34 @(cross(V(clk) - thresh, dir) or initial_step) begin

35 aout = 0;

36 weight = 2;

37 for (i = `bits - 1; i >= 0; i = i - 1) begin

38 if (V(in[i]) > thresh) begin

39 aout = aout + fullscale/weight;

40 end

41 weight = weight*2;

42 end

43 end

44 V(out) <+ transition(aout + vmin, td, tt);

45 end

46endmodule